7nm以下,摩尔定律还有效么?晶体管要继续缩小,需要什么工艺?

Arnaud Furnemont

Arnaud Furnemont的演讲名为“From Technology Scaling to System Optimization”。简单的2D尺寸缩放已经放缓。设计工艺协同优化(DTCO)已导致标准单元高度降低,但随着单元高度降低,鳍片数量也随之减少,因此需要器件工艺优化以保持性能。依靠DTCO来微缩芯片面积仍然很重要,但我们还需要从系统工艺协同优化(STCO)的系统角度自上而下地进行面积微缩。

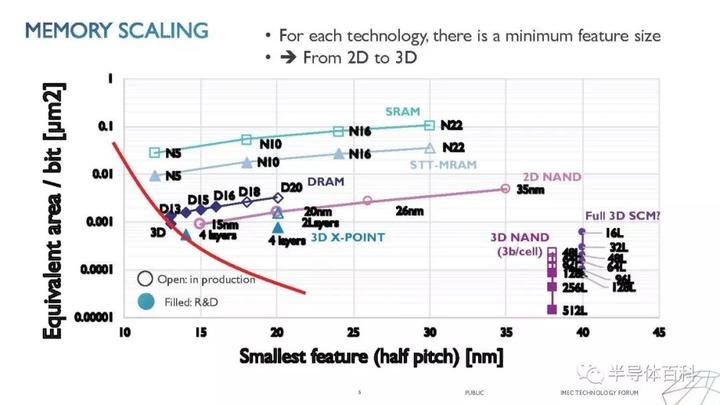

随着尺寸缩小,每种技术最终都会达到极限,并且需要从2D到3D的过渡。我们已经看到2D NAND转换到3D NAND时会发生这种情况。对于DRAM来说,他不相信D13/ D14节点下的电容器能够继续缩放下去,因此需要3D的解决方案。3D XPoint 存储器需要增加层数,逻辑工艺也必须转换为3D的。

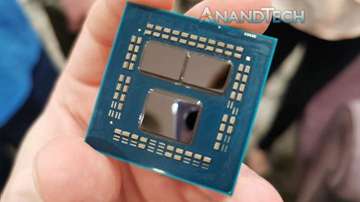

图1总结了工艺技术对存储器半节距的限制。

图1.存储器缩放的限制

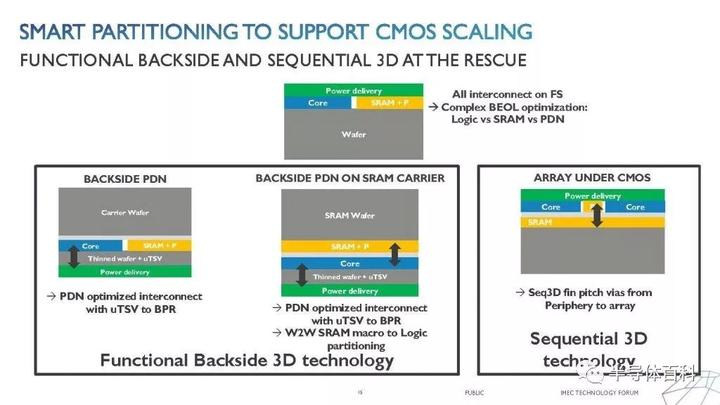

对于逻辑工艺的缩放,存在以一种比较智能方式:依照功能分区域分工艺制作。最后采用微型TSV工艺和薄型晶圆背面供电方式,将单独制造的SRAM和逻辑芯片集成起来,以提供更高度优化的解决方案,见图2。

Naoto Horiguchi

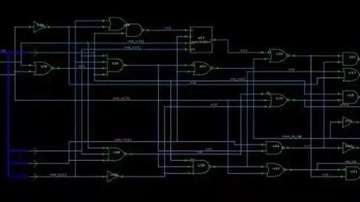

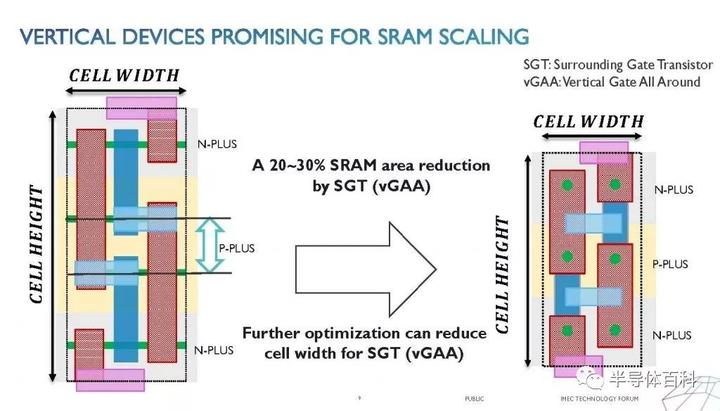

Naoto Horiguchi发表了一篇题为“Vertical Device Options for CMOS Scaling”的论文。论文的主要观点是,相比于以往水平放置的SRAM,垂直器件可以使SRAM阵列面积缩小,见图3。

图3.垂直晶体管SRAM

而且这项工作和之前的论文相符,因为通过制造仅SRAM阵列,工艺制程相对于完整的逻辑制程得以简化,例如SRAM仅需要大约4个金属互连层,而前沿逻辑制程需要12层或更多。

图4和图5展示了5nm节点级别的垂直SRAM阵列的基本工艺流程。蓝色的工艺步骤是EUV层(注意顶部电极是加粗蓝色字体(Nanowirepillars),但也是EUV层)。

这项工作也发表在VLSI Technology Forum [1],和通过图4和图5以及VLSI论文的分析可以得到更详细工艺制程的概括如下。

1.沉积N型外延层。

2.使用2张掩模版来制造高掺杂的N和P阱。

3.生长70nm厚的P型沟道外延层。

4.用EUV掩模和蚀刻工艺来形成8nm直径的纳米线柱阵列。蚀刻量是大约100nm接触到高掺杂阱中。

5.用EUV掩模和蚀刻工艺形成多组柱之间的浅槽隔离。

6.填充沟槽,然后回蚀刻氧化物凹槽,这暴露出纳米柱的上部区域以形成栅极。

7.进行化学氧化以产生和界面氧化物,然后进行HfO2和TiN的ALD沉积。

8.沉积钨(W)填充物,CMP平面化,然后进行凹槽蚀刻。

9.EUV掩模图形化和蚀刻以形成栅极,然后进行氧化物填充。

10.EUV掩模图形化,蚀刻和W填充以产生底部栅极接触。

11.EUV掩模图形化,蚀刻和W填充以产生交叉耦合。

12.沉积,图形化和蚀刻阻挡层,然后选择性外延SiB,以形成PMOS的顶部源极/漏极。

13.沉积,图形化和蚀刻阻挡层,然后选择性外延SiP,以形成NMOS的顶部源极/漏极。然后沉积氧化物。

14.EUV掩模图形化,蚀刻和W填充以产生顶部电极。沉积并平坦化ILD氧化物层。

15.EUV掩模图形化,蚀刻和W填充以产生栅极接触。

16.EUV掩模图形化,蚀刻和W填充以产生顶部电极接触。

17.沉积并平坦化氧化物,使用EUV掩模和蚀刻来形成金属1沟槽,然后填充铜并抛光。

18.EUV掩模图形化,蚀刻和W填充用于制作超级通孔。

19.EUV掩模图形化和蚀刻用于制造金属2和通孔2,然后填充铜并抛光。

该流程用于制作垂直SRAM测试器件。完整流程将包括至少两个以上的金属层,并且可能包括用于ESD保护的一些处理。该阵列可以与逻辑芯片和背面配电集成在一起,如图2所示。

Zsolt Tokei

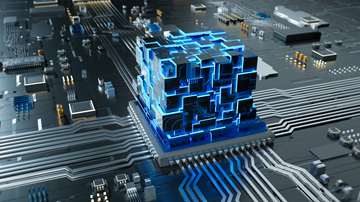

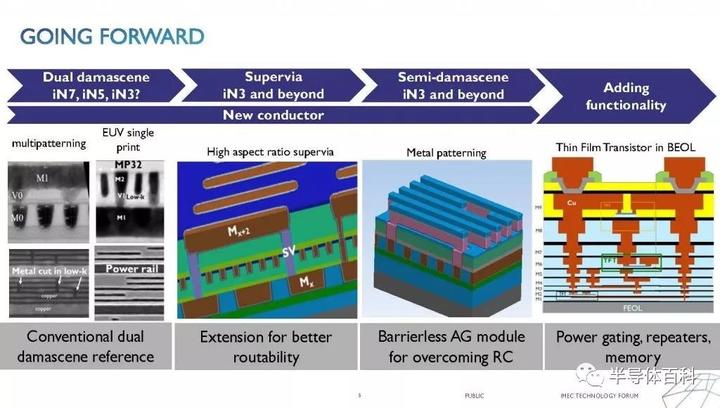

Zsolt Tokei发表了一篇论文名为“3nm Interconnects and Beyond: A toolbox to Extend Interconnect Scaling”。为了继续缩小与电阻- 电容(RC)的互连问题,需要解决成本,工艺漂移和机械稳定性问题。图6总结了之后的方向。

图6.之后的方向

为了更好的布线,传统双大马士革工艺会引入了超级通孔技术。为了降低RC delay,又会采用无阻挡层并且金属间有“气隙”(Air gap)的金属互联工艺(大概是用“半大马士革工艺”制作)。此外,还有可能将薄膜晶体管集成到BEOL中以增加其他功能。

半大马士革工艺流程如下:

1.在电介质膜中图案化并蚀刻通孔开口。

2.用钌(Ru)填充通孔并继续Ru沉积,直到在电介质上形成Ru层。

3.然后将Ru掩蔽并蚀刻成金属线。

4.在金属线之间形成“气隙”。

Ru的底部虽然有Ti粘附层(可能提高电阻值),但是通孔与金属线界面是连续的Ru,这减小了电阻,并且气隙减小了层间电容。Zsolt不愿意透露“气隙”的制作工艺,但我猜可能会是先均匀沉积一种薄膜,然后用另一种沉积来夹断封口并形成“气隙”。

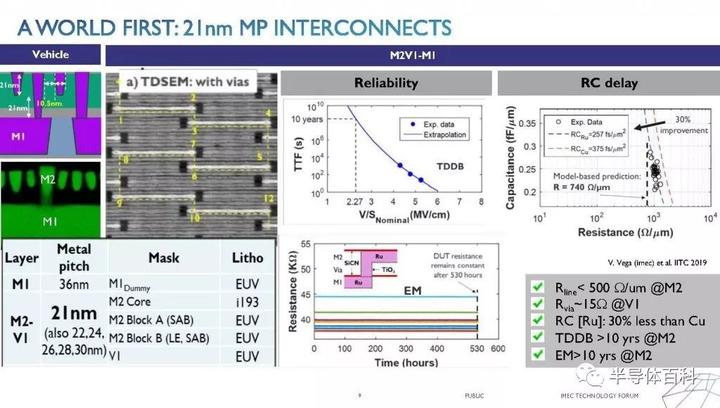

这项技术已经用于制造了世界上第一个21nm节距的金属互连层。图7总结了结果。

图7. 21nm间距互连

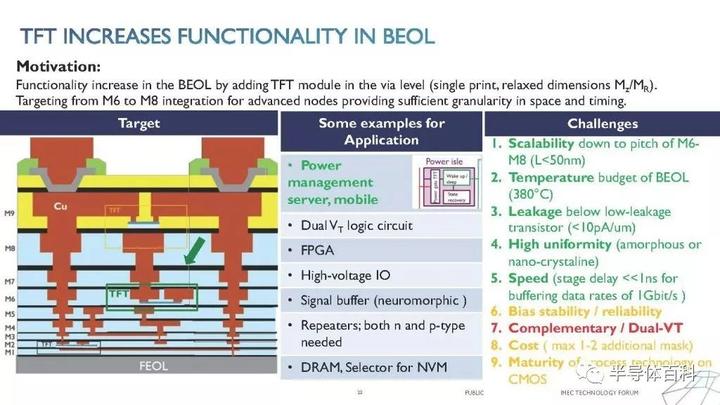

图8示出了BEOL中的薄膜晶体管(TFT)并描述了一些应用。

图8. 后段薄膜晶体管

结论

IMEC继续开展尖端研究,以支持持续微缩和改善半导体性能。

原文来自公众号半导体百科