5G或促使定制ASIC替代FPGA:5G基站可能放弃FPGA、改用ASIC

5G将带来巨大的成本和功耗问题,因此,业界有一种观点,认为5G基站所采用的FPGA平台需要向ASIC过渡。那么,这样做的原因是什么?如何在不牺牲FPGA灵活性的情况下,以经济高效的方式完成这项工作呢?本文将就这些内容进行讨论。

正如全球最大运营商中国移动执行副总裁李政茂在今年的世界移动大会(MWC)上所说的那样:5G所需的基站数量是LTE的3倍,5G的功耗也是LTE的3倍,而成本则是为LTE的4倍。

确实,这些成本/功耗方面的考量意味着:严重依赖FPGA和DSP的传统3G / 4G蜂窝基础架构方法难以应对5G的需求。而蜂窝网络设备制造商正在转向定制的ASIC来平衡毫米波的(mmWave)覆盖范围小、标准的低延迟、高吞吐量、大规模使用MIMO,以及多个天线的应用需要,从而无需衰减信号即可实现mmWave。

权衡:FPGA、DSP和ASIC

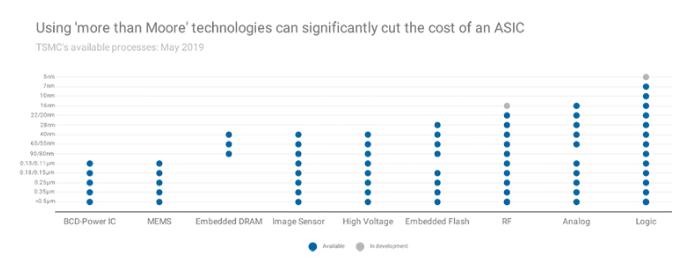

FPGA带来了灵活性,并在非常庞大的用户群中分担了NRE成本,它们还将开发工作限于配置它们所需的固件。但这是以晶体管冗余、高功耗和降低的时钟性能为代价的。确实,新一代SoC FPGA具有5G的许多数字组件所需的性能,但它们并不总是能够满足低功耗和低成本的需求(见图1),而且有时将不具备所需的逻辑或片上存储器容量。

图1:台积电在所有功能上的可用制程工艺

除了FPGA,也可以使用数字信号处理(DSP),例如使用Tensilica / CEVA的软件。但是,尽管仍具有灵活性,但与ASIC的硬连线逻辑相比,DSP需要更加强大的处理能力和更高的功耗。

因此,向ASIC的转变是蜂窝网络基础设施领域的一个发展趋势。在过去的一段时间内,特斯拉,Facebook,亚马逊和谷歌频频发布用于人工智能和自动驾驶汽车的ASIC,这些新闻都已成为主流媒体的头条,可见,ASIC在物联网、医疗设备和汽车控制系统等较小、低成本的利基应用中同样普遍。使用较旧的“超越摩尔定律”制程可提供具有成本效益的ASIC,从而平衡例如功耗、性能和芯片尺寸,但仍可以融入诸如RF或MEMS传感器之类的功能。

从FPGA设计移植

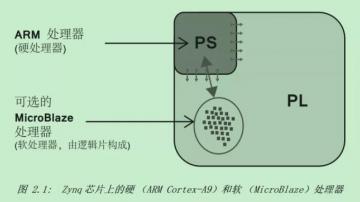

从带有RF SoC的FPGA(例如Xilinx Zynq)的迁移将带来可观的NRE成本(见图2)。类似地,使用许可IP内核将在降低风险和成本方面起很大作用。为了更清楚地了解这种情况,可以在Zynq UltraScale +的技术参考手册中找到许多Zynq IP的描述。

图2:ASIC与FPGA / DSP相比,可以优化晶体管的数量、时钟周期、生产成本和功耗,而ASIC在软逻辑设计中的性能与FPGA相同,但可以减小一到两个制程节点。

处理器内核、内存接口和外围设备分别可从Arm,Synopsys和Cadence获得。高速串行接口(SerDes PHY)和数据转换器可从多家供应商获得许可,包括Synopsys、Cadence或Rambus(包括但不止这些供应商)。

同样,关键IP可以从第三方获得许可,以替换FPGA供应商特定的IP。这包括一系列软IP,例如FEC加速器,数字下变频器(DDC),数字上变频器(DUC),奇异值分解(singular-value decomposition,SVD),浮点单元(FPU),矩阵数学引擎和快速傅里叶变换(FFT)核心。

诸如“ Design & Reuse”之类的网站是搜索此类IP的绝佳途径。

在从FPGA移植到ASIC的过程中,ASIC供应商将与客户合作,确保遵循良好的ASIC设计规范,例如使用时钟、复位和编码样式,并确保其设计符合以下要求:测试(DFT)友好。通常还会提供其他服务,以采用客户的高级系统模型并将其转换为适用于SoC的高效硬件加速器。

增加ASIC的灵活性

FPGA的主要优势始终在于其灵活性,例如,随着算法的改进或需求的变化,它具有更新硬件加速器的能力。传统上,这是通过合并高端DSP内核(例如来自Tensilica和Ceva的内核)或通过合并其他高端Arm MCU(如已经在FPGA设计中被广泛采用的A53和R5内核,当然不止这两种,还有很多其它内核)来解决的。添加这些额外的Arm MCU还可以简化软件开发。

但是,来自Achronix、Flex Logic和Menta的新一代eFPGA(嵌入式FPGA)架构为在定制ASIC中实现FPGA逻辑的灵活性提供了第三条途径,通常情况下,这些方案每平方毫米的硅仅提供数千个逻辑元件,因此使用它们可以抵消一些ASIC的省电和节省成本的好处。不过,我们建议您谨慎使用它们,以“摆脱困境(get out of jail card)”。

合并mmWave频率

5G的关键要素之一是合并mmWave频率,可提供更大的带宽。频率分配因国家/地区而异,因为美国的FCC发放了28 GHz、37 GHz和29 GHz许可频段(组合带宽3.85 GHz)以及从57GHz到71 GHz的14 GHz免许可频谱。

对于10GHz至80 GHz的mmWave RF ASIC,55nm至22 nm的CMOS制程工艺可以提供适合许多5G应用的性能。较小的节点用于实现数字波束成形、集成基带处理和嵌入式处理器内核所需的无关紧要的数字逻辑功能。

但是,对于这种类型的应用,完全耗尽的绝缘体上硅(FD-SOI)具有优于体硅CMOS工艺的优势,包括在给定的功率预算下改善了噪声系数(NF)、更高的RF输出功率、更好的通道隔离以及通过自适应体偏置技术来降低功率的能力。而且,尽管使用FD-SOI会增加成本,但可以在相控阵等应用中改善这种情况,因为相控阵的改进NF和每个设备的更高功率可能意味着需要更少的RF芯片。

平衡5G成本

5G在功率、成本和网络覆盖范围方面带来了若干挑战,因此促使蜂窝网络基础架构领域从3G / 4G系统中使用的FPGA / DSP转向更适合的ASIC。

Tesla、Facebook和Google之类的公司都已成为数十亿美元ASIC开发的头条新闻拥有者,但是这些都是用于AI和自动驾驶设备的,在这些设备中,最先进的技术至关重要。5G设备不需要相同的尖端技术,使用ASIC方法可以显着降低成本。

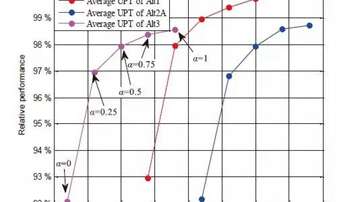

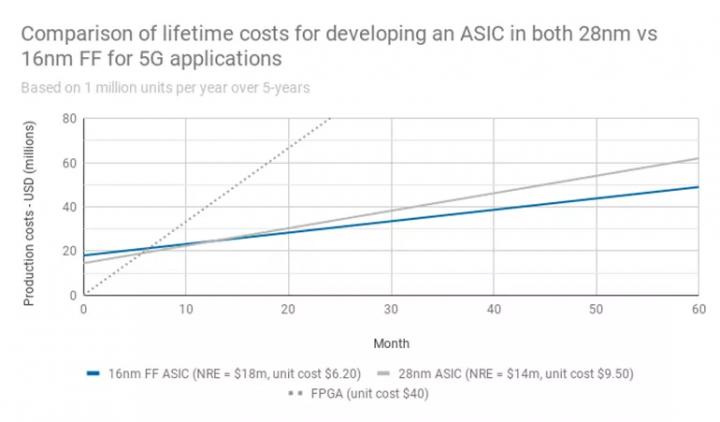

例如,如果我们看一下5G设备的需求,可以假设开发一个16nm FinFET ASIC的NRE成本(包括IP许可、开发和产品化)约为1800万美元,单位成本(基于芯片尺寸、封装、测试时间)大约为6.20美元。而开发22nm/28nm ASIC的NRE成本约为1400~1500万美元,单位成本约为9.50美元。

与之相比的是FPGA解决方案,例如Xilinx的用于通信应用的UltraScale +(在Digi-Key上单个单元的价格为975美元),该解决方案没有NRE,并且预期的批量成本约为30~50美元。

假设每年生产100万个器件(保守数字),则16纳米FinFET器件在短短13个月后最具成本效益(见图3)。

图3:虽然具有更高的NRE,但16纳米FinFET ASIC使其在短短13个月后便成为了低成本的选择。该图假设每年使用100万个单位,使用28纳米ASIC的NRE成本为1400万美元,而FPGA的单位成本为40美元。

显然,随着我们转向尖端的光刻工艺(例如10nm),PHY、ADC、DAC和掩模的IP许可的NRE成本将发生巨大变化。如果使用7nm,成本还会更高。

但是,尽管5G用的数字芯片需要7nm到40nm的制程,但值得注意的是,使用ASIC的软逻辑设计的性能与缩小一到两个制程节点的FPGA的性能大致相同。考虑到这一点,22nm /28nm ASIC将提供与16nm FinFET FPGA相似的逻辑性能,从而降低成本并降低5G应用的功耗。

除此之外,Xilinx UltraScale + FPGA中使用的Arm IP可以在ASIC中使用,这意味着可以维持与Xilinx器件兼容的软件(以及对软件的投资)。因此,尽管与FPGA相比灵活性降低了,但成本和功耗却成为蜂窝网络设备制造商转向定制ASIC、以满足5G需求的令人信服的理由。

来源:本文由公众号半导体行业观察(ID:icbank)翻译自「Microwaves & RF」,作者:Ian Lankshear