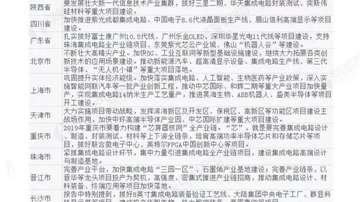

芯片封装的新技术方向:3D封装、小晶片、更多扇出技术

一、先进封装使用的主要技术

我们很难列出所有的先进封装类型,但可以列出一些目前使用的主要技术:

• 3D-IC:在开发真正的3D封装方面取得了多年的成功之后,业界正在推出新版本的内存逻辑和逻辑集成逻辑技术。这使得混合芯片架构、SRAM立方体和其他技术成为可能。

• 小晶片(Chiplets):使用小晶片,您可以在库中获得模块化芯片或小晶片的菜单。然后,将芯片组装到一个封装中,并使用一个“模具到模具”互连方案将它们连接起来。

• 在基板封装上扇出:这些技术将支持高带宽内存(HBM),而有些技术将攻破亚微米的线宽/间距壁垒。

以上的每种技术都面向不同的应用。不过,一般来说,这些和其他先进封装类型背后的想法是一样的,即在同一个封装中集成更多的裸芯片(die),这是一种异构集成的形式。这种异构形式反过来又可以使封装能够以较小的形状系数执行特定的高级功能。

异构集成还有其他的含义。它正在成为IC缩放的替代方案。在单片集成电路上包含更多的晶体管在每个新节点上变得越来越困难和昂贵。

另一种获得扩展好处的方法是将多个先进的芯片放入一个IC封装中。

解决系统中持续存在的内存瓶颈是先进封装背后的另一个驱动力。在系统中,数据在处理器和存储器之间移动。但这种交换有时会导致延迟和功耗,这个现象被称为内存墙。

“这个世界正在驱动更多的系统数据。因此,处理器需要大量的内存。“内存和处理器必须非常接近,”ASE的业务开发高级副总裁RichRice说。“因此,无论是2.5D还是使用基板的扇出方式,您都需要能够支持它的封装解决方案。这也可以是像package-on-package这样的pop结构。您将移动内存放在应用程序处理器的顶部,但使用的是非常密集的互连。”

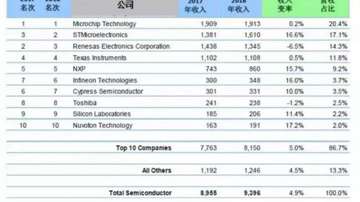

无论采用何种技术,业界都需要密切关注IC封装。根据Yole D_Developpement的数据,整个IC封装市场预计在2019年达到680亿美元,比2018年增长3.5%。根据Yole的数据,在这些数字中,先进封装预计在2019年增长4.3%,而传统封装增长2.8%。

更多2.5D/3D和小晶片

集成电路封装的重要性有几个原因。

首先,封装一个芯片,防止它被损坏。封装还将器件连接到电路板上。

其次,智能手机和其他产品需要小尺寸的芯片,这需要具有良好电气性能的小空间的、小间距的封装。

第三,在某些情况下,器件制造商需要一个执行特定功能的小型多芯片封装,有时也称为封装内系统(SIP)。例如,您可能需要将通信设备与物联网或传感应用程序的某些控制电路集成。ASE的赖斯说:“在SIP方面,还将看到大量的异构集成。”

第四,客户继续接受先进封装技术来解决各种问题。“先进的封装技术,如2.5D、3D TSV、高密度扇出和低密度扇出,将继续他们目前的应用。我们将继续看到封装所有领域的材料、薄型和电气性能的逐步改善。”AMKOR公司研发副总裁Ron Huemeller说。

多年来,该行业一直在开发先进封装技术,以解决系统中的其他挑战,如内存墙。在当今的内存层次结构中,SRAM集成到用于缓存的处理器中。DRAM用于主存储器,是独立的,位于一个双列直插式内存模块(DIMM)中。磁盘驱动器和基于NAND的固态存储驱动器(SSD)用于存储。

今天的存储器分层结构仍有一些挑战,特别是在高端。“人工智能、机器学习和数据中心领域的客户面临着无法获得足够内存的挑战。可以是片上存储器,也可以是片外存储器,封装外存储器。“GlobalFoundries的后Fab开发和运营副总裁David McCann解释道。“这对片上存储器的作用是使芯片尺寸增大。这会增加成本。”

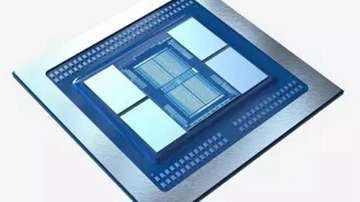

为了帮助解决服务器等高端应用程序的问题,业界正朝着2.5d技术方向发展。在2.5D中,裸芯片(die)被堆叠在中介层顶部,插入器通过硅通孔(TSV)合并。中间层充当芯片和板之间的桥梁,提供更多的I/O和带宽。

在2.5D封装的一个实例中,供应商可以合并一个FPGA和HBM。针对高端系统,HBM堆叠和DRAM芯片相互重叠,实现更多I/O接口。例如,三星最新的HBM2技术包括8个8Gbit DRAM芯片,这些芯片使用了5000个TSV进行堆叠和连接。

总的来说,它支持307Gbps的数据带宽。相比之下,根据Xilinx的数据,使用传统DRAM时,四个DDR4 DIMM的最大带宽为85.2Gbps。在大多数2.5D版本中,芯片都是并排放置的,尽管在这些芯片上使用“支柱”技术正在进行一些开发。但是在这两种情况下,内存都比传统的平面设计更接近处理器,而且到外部内存的吞吐量更快。

“我们正在解决内存延迟问题,通过使内存非常接近,并在芯片之间创建一个巨大的并行接口,”McCann说。McCann指出缺点是插入器(中介层)相对昂贵。“这增加了成本,但它使我们能够在芯片之间实现密集的互连。”

超过2.5D,下一个重大的飞跃是3D IC或垂直堆叠,这保证了更快的访问速度和更低的内存和处理器之间的延迟。

3D是一个过度使用的术语,它对不同的人意味着不同的事物。有些人称2.5D为3D技术。从技术上讲,DRAM堆栈也是3D的,它是由电线连接的。

“传统上,3D-IC是指通过有源芯片的硅通孔。人们正朝着不同的方向采取这一措施,”ASE的赖斯解释说。“有无源的中介层,还有一些具有一定电路或功能级别的活动中介层。你在上面放置裸芯片,中介层是有源的,这意味着它可能有一些电源电路或内存。”

3D-IC技术并不新鲜,它已经开发多年了。例如,在2011年,美光(Micron)宣布了混合内存立方体(HMC),它将内存芯片堆叠在逻辑芯片上。2018年,美光公司由于利用率不高而放弃了HMC。

3D-IC的另一种形式是相互堆叠逻辑芯片。“3D的逻辑到逻辑不是新的。Yole的分析师Santosh Kumar说,“有很多来自不同厂商的R&D原型,但还没有生产。”当然,成本是主要的挑战。但也存在技术问题,如热管理、已知合格的芯片、测试和可靠性。”

在许多这些问题上似乎都取得了进展,这最终可能使三维集成电路成为现实。供应商现在正在讨论市场中的各种产品。例如,格罗方德(GlobalFoundries)正在开发一个“SRAM多维数据集”。通常,SRAM与处理器集成,但SRAM占用了大量的面积。SRAM芯片不是集成SRAM和处理器,而是堆叠在处理器顶部并与TSV连接。产生的器件是一个SRAM/逻辑堆栈。

目标是缩短处理器和SRAM之间的互连距离,从而减少延迟。“我们现在有更小的芯片,”格罗方德的McCann说。“总成本可能大幅下降。”

除此之外,格罗方德还开发了一种2.5D/3D技术的组合,该技术承诺能够更快地访问内存。例如,在2.5d包中,您将在一个插入器上放置三个独立的内存堆栈。第一个是SRAM立方体,位于插入器上两个HBM堆栈之间。

与此同时,英特尔最近推出了一种叫做“Foveros”的新3D封装技术,这不是一种产品,而是一种支持多芯片封装的技术。它允许将芯片分解成更小的IP块或芯片,这些块或芯片通过活动的中介层连接。

英特尔表示,它已经解决了阻碍3D-IC发展的技术障碍。“第一件事是解决两到三个棘手的问题,如热和电力输送。这是一个挑战,而且还不容易解决,”英特尔的高级首席工程师威尔弗雷德•戈麦斯说。“我们已经想出了新的创新来解决这个问题。”

总之,英特尔的Foveros支持更高级的异构集成形式,即使不是扩展器件的另一种方式。英特尔表示,从理论上讲,这项技术可以与集成芯片系统(SOC)的功能相匹配。

英特尔没有放弃芯片缩放,但Foveros提供了一些新的选择。例如,使用这种方法,英特尔最近推出了一个新的混合CPU平台,代号为“lakefield”,它将一个10nm处理器核心与英特尔的四个Atom处理器核心组合成一个小的封装。

英特尔和其他公司正在为小晶片模型铺平道路。在小晶片中,将不同模块(如乐高积木)组合在一起的想法已经讨论了多年,但很少有人实现了。

“小晶芯片的动机是以较小的技术增量工作,要么利用现有硅中的现有功能,要么创建更小的构建块,根据需要进行混合和匹配,以实现更好的系统优化、更低的成本和更快的上市时间,”Kandou Bus的首席执行官Amin Shokrollahi说。“小晶片将开启一个全新的硅创新时代,使小型企业更容易竞争。”

Kandou Bus开发了一种互连结构,作为封装或模块中芯片的一种模对模互连。该公司正与市场中的几个团体合作。那么,小晶片什么时候起飞呢?“我们已经为使用我们的Glasswing Serdes技术的产品制造了许多原型,我们预计到2019年中期会批量生产,”Shokrollahi说。“但是,广泛采用小晶片的策略和开发可互操作的小晶片可能还需要几年的时间。”

“关于如何设计、制造、组装和测试芯片,然后在现场支持这些解决方案,仍然存在许多问题。当芯片来自不同的公司或用不同的代工工艺制造时,还存在其他挑战。Kandou已经解决了一些接口问题,至少从SERDES的角度来看是这样的,但是我们确实看到需要更广泛的行业参与和合作来创建一个共同的框架,”Shokrollahi说。

Marvell Semiconductor的网络CTO Yaniv Koppelman同意这一点。“今天,我们在交换机上使用各种类型的小晶片,您可以用不同数量的小晶片填充多种类型的馈送和速度。不过,我们发现,在技术上,该行业还没有准备好采用这种方法。我们还没有达到临界质量。这就是为什么你开始看到XSR(超短程),它是一个来自100GigPAM-4的接口,你可以收缩它。我们还看到了封装光学器件的选项,它可能驱动两个芯片之间的标准接口,尽管不一定在同一家公司。”

更多的扇出技术

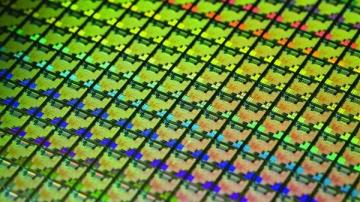

与此同时,另一种称为扇出晶圆级封装(FOWLP)的封装技术也正在形成势头。在扇出中,裸芯片是在晶圆上封装的。扇出不需要中介层,因此比2.5D/3D便宜。

但封装客户需要HBM,HBM必须要2.5D/3D封装。这很可能会改变,该行业目前正致力于集成和支持HBM的高密度扇出封装。这些封装可以为客户提供新的、更便宜的HBM技术选择。

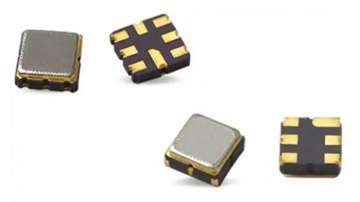

有或没有HBM,扇出都涉及相同的基本结构。“在FOWLP中,芯片被嵌入到环氧树脂模塑料中,然后在晶片表面形成高密度再分布层(RDL)和焊球,以形成重组的晶片。”BrewerScience晶圆级封装材料业务部门的技术总监KimYess在博客中解释道。

RDL是铜金属连接线或连线,它们将封装的一部分与另一部分进行电气连接。RDL是通过线宽和间距来测量的,线宽和间距指的是金属连线的宽度和间距。

有三种类型的扇出包:chip first/face down;chip first/face up;chip last或RDL first。

最初,扇出没有将中介层作为基板。然而,由于裸芯片和环氧树脂模化合物之间的不匹配,无基板的扇出封装较容易发生翘曲和/或应力。

所以最近封装公司开始在基板上发展扇出技术。该流程类似,但封装使用了BGA基板,这提高了器件的可靠性。“有多种方法可以将基于晶圆的扇出技术结合到基板平台上。”Amkor的Huemeller说。“根据裸芯片的高度和电气性能要求,低密度和高密度都在今天被使用。它们通常都被放置在现有的基板上,这些基板包含较少的层,具有更大的功能,既可以降低成本,又可以扩大供应链。这些通常是BGA基板,但HDI板正在考虑中。”

在2016年,ASE引进了一种称为“基片扇出芯片”(FOCoS)的技术。针对服务器应用,FOCoS的第一个客户在同一个封装中集成了单独的16nm和28nm芯片。封装有四个金属层,线宽/间距组合为2-2.5微米。

初始FOCoS封装基于chip-first工艺。定于今年推出的下一代FOCoS支持HBM。该版本能够提供2-2微米的线宽/间距,未来将提供1.5-2微米的线宽/间距。

“ASE正与客户合作开发最新版本的FOCoS芯片,它可以支持HBM2内存,”ASE工程高级总监约翰•亨特说。“它适用于异构和同构的服务器应用,以及AI和Chiplet应用。它旨在成为这些市场的中介解决方案的替代方案。它提供了一种低成本的解决方案,实际上比硅中介层结构具有更好的电性能和热性能。”

FOCoS使用BGA基板。“它基本上与标准BGA封装上使用的基板类型相同,也与2.5D中介层封装上使用的基板类型相同,”亨特说。“BGA基板提供封装中的第二级“扇形输出”,从更细的FOCoS凸点间距到具有有效成本结构的标准电路板组装间距。”

同时,TSMC也在朝着类似的方向移动。台积电的扇出封装技术,称为InFO,正在苹果最新的iPhone中使用。现在,这家代工巨头正在开发一种新的基板技术,称为IInFO_MS。InFO_MS是支持HBM的平台。”TechSearch International总裁Jan Vardaman表示。”今年应该投产。”

“尽管InFO_MS处于研发的早期阶段,但这项技术的目的是将HBM直接集成到基板上,而无需中介层。但从技术上来说,要做到这一点并不容易,”Yole的分析师FavierShoo说。

台积电也正在开发一种超高密度的InFO技术,将扇出带入到亚微米的状态。到目前为止,最先进的扇出将RDL降低到大约2-2微米的线宽/间距。然而,台积电正准备开发0.8微米的InFO与更精细的几何尺寸。“这是相同的架构。这种互连密度对于带宽改进很重要。台积电研发部副总裁Doug Yu表示:“我们还尽可能减少了寄生效应。”

▲ 叠层多尺度die-stencil填充概念

(资料来源:Brewer Science)

这个技术还有其他好处,具有较小临界尺寸的布线层能够减少扇出封装中布线工艺级别的总数。这反过来又降低了总封装成本,提高了产量,”Veeco全球光刻应用副总裁Warren Flack说。“目前,1微米RDL的体积很小,但我们预计在未来几年它将显著增加。”

为了在先进封装中对RDL层进行布线设计,该行业使用各种光刻系统。在封装中设计最好的RDL特性是很有挑战性的。

“最先进的封装光刻系统的设计最小特征是2微米或更高,”Flack说。“要想获得较小的特征,就需要用较短的波长曝光,并具有较大的透镜数值孔径(NA)。这些先进的扇出封装的主要光刻挑战是:成像具有高纵横比的亚微米RDL;最小化裸片移位产生的叠加误差;极弯曲的基板处理;以及支持非常大的晶圆级封装尺寸上的2.5D芯片。良率和生产率将推动采用先进的扇出封装,只有非常高的ASP设备才能承受这种先进的封装方法。”

在扇出技术中,裸芯片位移是一个更大的问题。在工艺中,裸片往往在环氧材料中移动,导致位置变化和其他问题。

布鲁尔科学公司正在研究解决这个问题的方法。这项技术在裸片中使用一层薄膜,就像模版一样工作。

“裸片模版是使用传统EMC扇出方法的替代方法。它不需要使用典型的EMC来制造构成的基板。这是有利的,因为它减少了通常用EMC扇出技术观察到的翘曲变形,并且能够灵活地将各种裸片集成到封装中,与它们的尺寸和特性无关,”Brewer的Yess说。

因此,展望未来,客户将有新的和各种不同的先进封装选择表。这些技术令人印象深刻,至少在纸面上是如此。但是和以前一样,将它们集成到系统中说起来容易做起来难,特别是对于要求苛刻的客户来说,和在合适的价位上。

原文来自智慧产品圈